- Home

- Products

- Summary & Overview

- Bus Analyzer

- Diagnostic System

- Interface Cards

- FireRepeater

- Connectivity

- IP Cores

- Software

- Accessories

- Solutions

- Support

- News

- Contact

- Company

- Mil1394

- Sitemap

- Search

The FireCore Extended IP package is targeted at applications with up to 3200Mbps data transmission and high data throughput requirements. It combines FireLink Extended and FireGate into one core. FireLink® Extended features OHCI-compliant DMA engines and supports non-PCI, PCI and PCIe host bus interfaces.

Several markets can make use of the FireCore Extended core including Aerospace & Defense, Industrial and Consumer Electronics. As a special option, the FireLink® LLC offers firmware Support for the AS5643 (Mil1394) protocol. While current implementations require significant host software support, FireLink® can support this layer with significantly better timing as well as reduced host resource utilization.

Examples of typical applications in aerospace & defense for the FireCore include command & control systems for space-based vehicles, missile guidance platforms, fighter aircraft flight control, as well as its implementation in avionics & IFE platforms for business and commercial aircraft.

The industrial applications of FireLink® are quite broad and include robotics, machine vision, wide format digital printing and medical imaging. Specifically the Extended version targets all implementations that try to benefit from PCI-based OHCI implementations.

DapTechnology supports its IP cores on a wide variety of FPGA families. At the moment of writing the following platforms are supported but please don't hesitate to contact us for the very latest information:

Please contact DapTechnology directly to verify availability of specific functionality on your target platform!

There are several advantages when using FPGAs to implement a complete 1394 I/O interface. Some of these are:

FireCore is designed highly configurable. We can preadjust key functions and components (speed, ports, target platforms, ...) as compilation parameters and so optimize the resources needed to meet customers needs. Such configuration parameter will be defined in close consultation with you so order to custom tailor the solution. Please note that due to differences within the various FPGA platforms certain functions might not be supportable on all target FPGAs. Please consult with our sales staff on availability.

FireLink® Extended and Basic both contain the same LLC related functional blocks and with that ensure functional standards compliance as well as interoperability with off-the-shelf physical layer devices (assuming PHY layer I/O compliance).

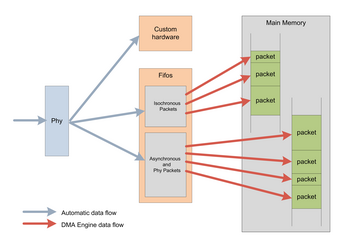

The big difference between the two versions lies in the host connectivity interface. FireLink® Extended utilizes the architectural and performance-based benefits of the DMA-capable communication interface. DMA transfers copy blocks of memory from one device to another and, while the CPU initiates the transfer by issuing a DMA command, it does not execute it. Advanced bus designs such as PCI typically use bus mastering DMA where the device takes control of the bus and performs the transfer itself. In an embedded processor or multiprocessor system-on-chip, it is a DMA engine connected to the on-chip bus that actually administers the transfer of the data. Another difference is that the Extended version does not include iso ports as the DMA mechanism efficiently handles the iso data transfer.

FireLink® Extended uses such an advanced DMA-enabled interface. And FireStack® - DapTechnology’s own IEEE-1394 software stack – takes this concept even further with its consistent utilization of zero-copy data handling mechanisms. Together they form a very powerful combination aimed at complete system throughput optimization as well as minimization of system latencies and resource utilization.

FireGate is a fully IEEE-1394b-2008 compliant PHY Layer implementation. The main PHY layer related functional blocks ensure functional standards compliance as well as interoperability with off-the-shelf physical layer devices.

A key element of FireGate is its configurable PHY front end, i.e. the ability to customize several aspects of the PHY cable environment interface. During the configuration phase the total number of available PHY ports can be adjusted (max 16) and as well as the total number of PHY instances per FPGA device. Furthermore, the speeds supported by the PHY can be defined. The PHY speeds can be either predefined to support single network speeds (for example S100, S200, S400, ...). This reduces network speed negotiation times (only applicable if connected to a same-speed device). Alternatively, the PHY(s) can be configured to support speed ranges (e.g. S200 - S800) and limit the speed negotiation to those values).

Additionally, the PHYs also contain patented improvements over standard 1394 implementations. DapTechnology has been one of the very first companies to actively advocate such functionalities within PHY devices.

In FireLink® Basic the packet data flow is processor driven, i.e. any received/transmitted packets have to be read from or written to a Dual-Ported RAM Buffer by a processor. The Dual Port RAM Buffer is located inside the core and is customizable in size to accommodate for the maximum packet size. This concept is intended for small core sizes.

Received packets are stored in chained buffers which are prepared in host memory. A new buffer can be used for each packet, or multiple packets can be stored in one buffer. For certain applications, like camera streaming, the LLC is capable to stream the packet payload immediately into video buffers, with an absolute minimum of processor overhead

As the first vendor worldwide, DapTechnology offers a very unique, but extremely powerful addition to its standard 1394b link layer IP core (extended version only). Our active participation in SAE ASD AS-1A3 standards committee together with the close collaboration with many adopters of the this standard allows DapTechnology to, not only develop a fully standards-compliant extension to the LLC, but also go beyond and/or deviate from the current AS5643 standard.

The AS5643 package is designed to offload the AS5643 support from the host processor. The following features are supported in firmware:

Compared with other implementations using off-the-shelf 1394 LLC silicon (and AS5643 support implemented in SW) this AS5643 extension to the extended version of FireLink drastically improves the overall system performance, offloads the host processor and guarantees timing deadlines that otherwise can only be accomplished with real-time operating systems.

FireLink can also be paired with FireGate. With their respective AS5643 extensions they form the perfect PHY/LLC system on chip (SOC) solution for typical aerospace applications. Please contact DapTechnology if your requirements go beyond the current AS5643 specification. The flexible architecture of the AS5643 extensions allows for the integration and support of features/functions that were not considered in the AS5643 standard as they are not supported by standard silicon. Examples could be static LinkIDs (instead of the very dynamic NodeIDs), isochronous stream acknowledgements, Bus Reset suppression and static nodeID assignments (only suitable fully deterministic systems) as well as full System Integrity Management.

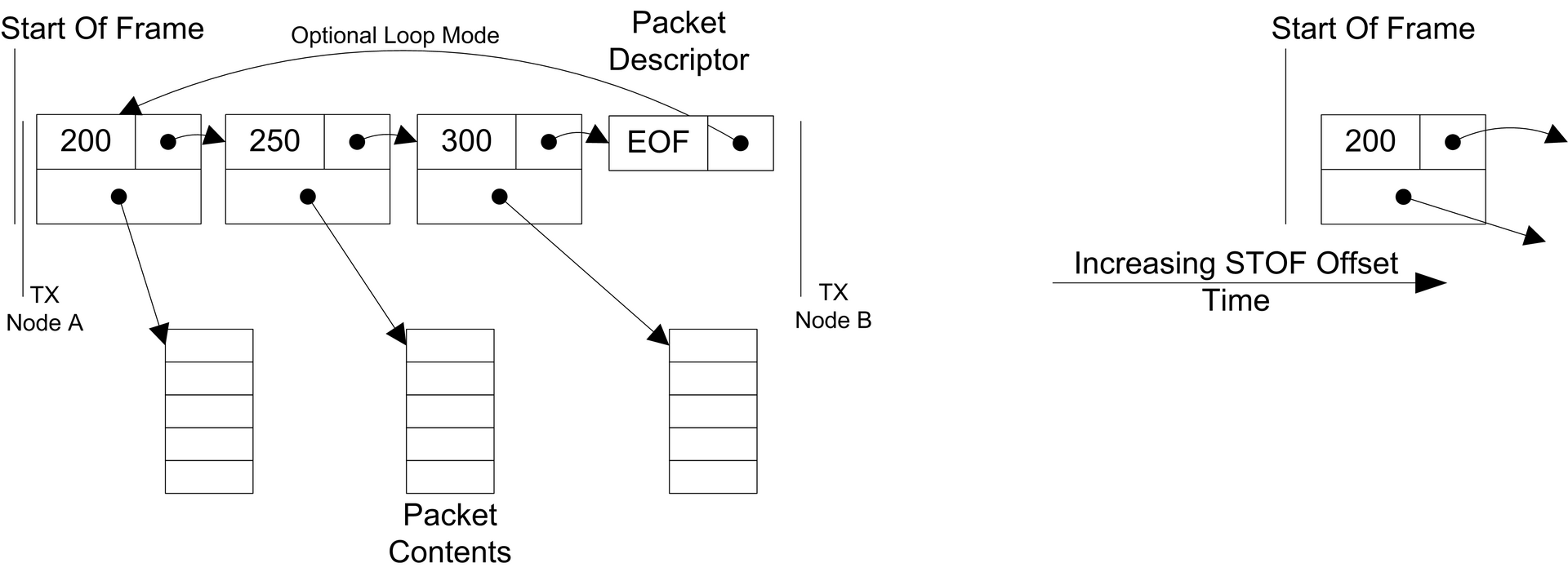

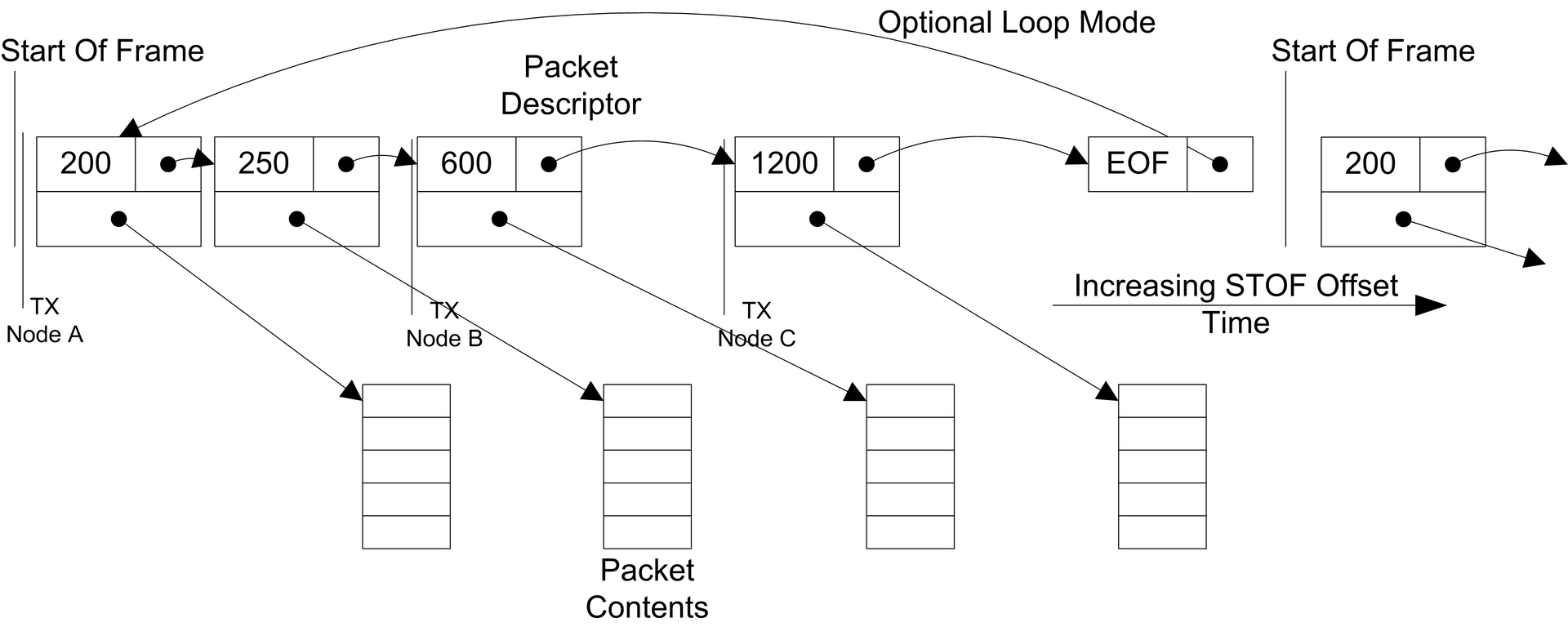

The AS5643 solution takes full advantage of the OHCI-like system architecture of the Extended version of the FireLink®. From an applications point of view the OHCI-like descriptor block model is perfectly suited for powerful transmission link lists for isochronous stream packets. Part of the descriptor is a 16-bit timing field which allows for a precise time adjustment for AS5643 transmit offset requirements. Additionally, the descriptor can be run in a looped mode in case a device has to transmit in every AS5643 time frame.

The same mechanism also allows transmitting messages from a single device but utilizing different node specific time slots. Such transmission lists can be perfectly used for simulation projects that may want to simulate an entire network’s traffic without physically using multiple bus devices.

Available under NDA only.

Please send an email to sales(at)daptechnology.com for more information.

|

FireCore Extended NetList |

Status: active |

|

FireCore Extended Source Code |

Status: active |

|

FireCore Extended Deployment |

Status: active |

Standard: 12 months, limited.

Options: Additional 1-year Support packages may be purchased.

All IP products will be supported on a 24 hours response basis and free of charge during the warranty period. For support questions please contact: sales(at)daptechnology.com

Of course you can also call us during our office hours from 9:00 until 17:00 hours (GMT +1:00). Contact Info

Please contact sales(at)daptechnology.com for current pricing.

| Country | Distributor | Phone | URL |

|---|---|---|---|

| Japan | Nacelle Co. Ltd. | +81-3-5921-5099 | www.nacelle.co.jp |

| United States of America | DapUSA, Inc | +1 480 422 1551 | www.dapusa.com |

| South Korea | Realtimewave Co. Ltd. | +82-31-698-2980/2 | www.realtimewave.com |

| all other countries | Dap Technology B.V. | +1-514-453-4111 | www.daptechnology.com |

Click here for a more detailed listing of our Sales Representations.

For the U.S.A., we have as representatives:

| Representative | Territory | Phone | URL |

|---|---|---|---|

| Dap USA Office Arizona | Entire United States of America | +1 480 422 1551 | www.dapusa.com |

To place an order for DapTechnology products, please print one of the following order forms and email it to the corresponding email address:

USA:

Dap USA, Inc.

sales(at)dapusa.com

Download order form

Or contact us by phone: +1 480 422 1551

Rest of the world:

Dap Technology B.V.

sales(at)daptechnology.com

Download order form

Or contact us by phone: +1 480 422 1551