- Home

- Products

- Summary & Overview

- Bus Analyzer

- Diagnostic System

- Interface Cards

- FireRepeater

- Connectivity

- IP Cores

- Software

- Accessories

- Solutions

- Support

- News

- Contact

- Company

- Mil1394

- Sitemap

- Search

The FireCore Basic is targeted for applications with up to S3200 data transmission requirements and for designs with a non-PCI Link Controller requirement. FireCore was designed to meet the general purpose and IIDC camera markets with higher speed and IEEE-1394-2008 Beta support not typically covered by other chip sets such as the Texas Instruments GP2Lynx (TSB12LV32). The FireLink Core therefore provides a seamless upgrade path to IEEE-1394-2008 Beta.

Several markets can make use of the FireCore Basic including Aerospace & Defense, Industrial, and Consumer Electronics. As a special option, AS5643 (Mil1394) protocol support is planned for FireCore Basic. While current implementations require significant host software support, FireCore will be able to support this layer with significantly better timing as well as reduced host resource utilization. Examples of typical applications in aerospace & defense for FireCore include command & control systems for space-based vehicles, missile guidance platforms, fighter aircraft flight control, as well as its implementation in avionics & IFE platforms for business and commercial aircraft.

The industrial applications of FireCore are quite broad and include robotics, machine vision, wide format digital printing and medical imaging. Finally, FireCore is ideal for use in Consumer Electronics equipment such as Set Top Boxes, DVD peripherals and High Definition A/V equipment.

DapTechnology supports its IP cores on a wide variety of FPGA families. At the moment of writing the following platforms are supported but please don't hesitate to contact us for the very latest information:

Please contact DapTechnology directly to verify availability of specific functionality on your target platform!

There are several advantages when using FPGAs to implement a complete 1394 I/O interface. Some of these are:

FireCore is designed highly configurable. We can preadjust key functions and components (speed, ports, target platforms, ...) as compilation parameters and so optimize the resources needed to meet customers needs. Such configuration parameter will be defined in close consultation with you so order to custom tailor the solution. Please note that due to differences within the various FPGA platforms certain functions might not be supportable on all target FPGAs. Please consult with our sales staff on availability.

FireLink® Basic consists of a fully IEEE-1394b-2008 compliant Link Layer implementation. All LLC related functional blocks ensure functional standards compliance as well as interoperability with off-the-shelf physical layer devices (assuming PHY layer I/O compliance).

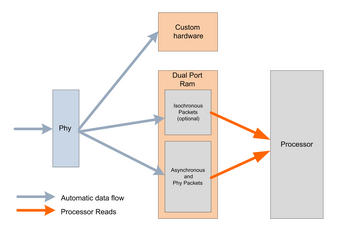

Essential to FireLink® Basic is its very simple host connectivity. Via simple 32 bit data/address bus R/W operations as well as control registers. Updates can be handled via a dual-ported RAM or direct register access. Since any communication with this DPRAM is host processor driven this interface is optimized for small/medium sized data (isochronous, asynchronous and PHY layer) packets as well as low bandwidth requirements. Just like sending large amounts of data via the I/O bus, an increased number of individual bus transactions negatively affect the overall interface performance. For transmission and reception of large isochronous streams (e.g. video and/or audio) alternate data paths are available by means of the ISO Transmit and Receive Ports. They allow connecting dedicated data generating/processing hardware directly to the transmit/receive engines of FireLink®. As these dedicated ports are bypassing the host main processor they are not restricted by performance limitations of the main host interface and therefore guarantee optimized data rates.

An additional benefit is the ability to customize several functional elements of the core. Since not all 1394 implementations require a full-featured 1394 interface (e.g. a pure IPv4 (IP over 1394) or AS5643 implementation using only asynchronous messaging can reduce FPGA footprint requirements by leaving out certain functional blocks like isochronous data ports, Cycle Timer and transmit, etc. from the deployed netlist. Likewise, an isochronous data transmitting video camera can omit a RX iso port as it is a dedicated data streaming device and the general purpose RX and TX buffer can be held small.

FireGate is a fully IEEE-1394b-2008 compliant PHY Layer implementation. The main PHY layer related functional blocks ensure functional standard compliance as well as interoperability with off-the-shelf physical layer devices.

A key element of FireGate is its configurable PHY front end, i.e. the ability to customize several aspects of the PHY cable environment interface. During the configuration phase the total number of available PHY ports can be adjusted (max 16) as well as the total number of PHY instances per FPGA device. Furthermore, the speeds supported by the PHY can be defined. The PHY speeds can be either predefined to support single network speeds (for example S100, S200, S400, ...). This reduces network speed negotiation times (only applicable if the entire network would use the same PHY). Alternatively, the PHY(s) can be configured to support speed ranges (e.g. S200 - S800) and limit the speed negotiation to those values).

Additionally, the PHYs also contain patented improvements over standard 1394 implementations. DapTechnology has been one of the very first companies to actively advocate such functionalities within PHY devices.

In FireLink® Basic the packet data flow is processor driven, i.e. any received/transmitted packets have to be read from or written to a Dual-Ported RAM Buffer by a processor. The Dual Port RAM Buffer is located inside the core and is customizable in size to accommodate for the maximum packet size. This concept is intended for small core sizes.

Received Packets are stored in the Isochronous or Asynchronous Receive Buffer or are routed to an Isochronous Receive Port or the Asynchronous Receive Port.

Available under NDA only.

Please send an email to sales(at)daptechnology.com for more information.

|

FireCore Basic NetList |

Status: active |

|

FireCore Basic Source Code |

Status: active |

|

FireCore Basic Deployment |

Status: active |

Standard: 12 months, limited.

Options: Additional 1-year Support packages may be purchased.

All IP products will be supported on a 24 hours response basis and free of charge during the warranty period. For support questions please contact: sales(at)daptechnology.com

Of course you can also call us during our office hours from 9:00 until 17:00 hours (GMT +1:00). Contact Info

Please contact sales(at)daptechnology.com for current pricing.

| Country | Distributor | Phone | URL |

|---|---|---|---|

| Japan | Nacelle Co. Ltd. | +81-3-5921-5099 | www.nacelle.co.jp |

| United States of America | DapUSA, Inc | +1 480 422 1551 | www.dapusa.com |

| South Korea | Realtimewave Co. Ltd. | +82-31-698-2980/2 | www.realtimewave.com |

| all other countries | Dap Technology B.V. | +1-514-453-4111 | www.daptechnology.com |

Click here for a more detailed listing of our Sales Representations.

For the U.S.A., we have as representatives:

| Representative | Territory | Phone | URL |

|---|---|---|---|

| Dap USA Office Arizona | Entire United States of America | +1 480 422 1551 | www.dapusa.com |

To place an order for DapTechnology products, please print one of the following order forms and email it to the corresponding email address:

USA:

Dap USA, Inc.

sales(at)dapusa.com

Download order form

Or contact us by phone: +1 480 422 1551

Rest of the world:

Dap Technology B.V.

sales(at)daptechnology.com

Download order form

Or contact us by phone: +1 480 422 1551